深入解析MIPS流水线 计算机系统结构的高效执行引擎

在计算机系统结构领域,处理器性能的提升一直是核心议题。其中,流水线(Pipelining)技术是一种将指令执行过程划分为多个阶段,并使多条指令在不同阶段重叠执行的关键技术,它极大地提高了指令吞吐率。MIPS(Microprocessor without Interlocked Pipeline Stages)作为一种经典的RISC(精简指令集计算机)架构,其设计的核心思想之一便是深度契合流水线技术,以实现简单高效的处理。

1. MIPS指令集与流水线的基础

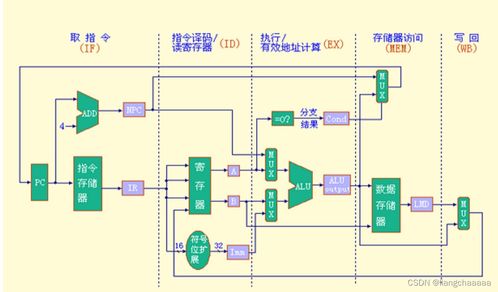

MIPS指令格式规整(如R型、I型、J型),指令长度固定为32位,且绝大多数指令在一个时钟周期内完成一个流水阶段的操作。这种简洁性使得流水线的实现变得清晰,避免了复杂控制逻辑带来的时序问题。一条典型的MIPS指令执行过程可被划分为五个经典阶段:

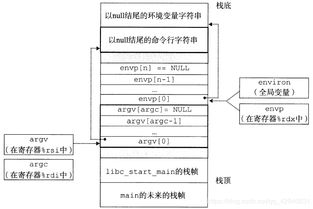

- 取指(IF):从指令存储器中读取指令。

- 译码(ID):解析指令,从寄存器堆中读取源操作数。

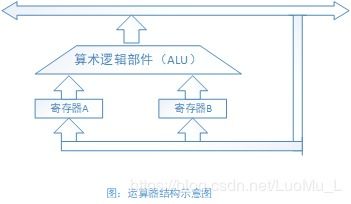

- 执行(EX):在算术逻辑单元(ALU)中进行计算或地址计算。

- 访存(MEM):访问数据存储器(针对Load/Store指令)。

- 写回(WB):将结果写回寄存器堆。

理想情况下,每个时钟周期都有一条指令完成(离开流水线),如同装配线一般,CPI(每条指令周期数)趋近于1,相比非流水线设计的CPI≥5,性能提升显著。

2. MIPS五级流水线的挑战:冒险(Hazard)

在实际运行中,指令间的依赖关系会破坏流水线的顺畅流动,这些阻碍被称为“冒险”,主要分为三类:

- 结构冒险:因硬件资源冲突导致。例如,单端口存储器在同一个周期内无法同时支持指令取指和数据访存。MIPS通过分离指令存储器和数据存储器(哈佛结构思想)或使用缓存来解决。

- 数据冒险:后续指令需要用到前面指令尚未产生的结果。例如,

ADD $s0, $t0, $t1后紧跟SUB $t2, $s0, $t3,SUB指令在ID阶段需要$s0时,ADD指令可能还在EX或MEM阶段。MIPS主要采用两种技术应对: - 前递(Forwarding / Bypassing):将ALU结果或访存数据直接从产生它的流水段(EX或MEM)的出口,绕道传送到需要它的流水段(EX)的入口,从而避免等待写回。这是解决数据冒险最主要和高效的方法。

- 流水线暂停(Stall / Bubble):当前递无法解决时(如Load指令后紧接使用其结果的ALU指令),控制逻辑会插入一个“气泡”(空操作),使流水线暂停一个周期,等待数据就绪。

- 控制冒险:由分支指令(如BEQ、J)引起。在ID阶段解析出分支目标地址之前,后续指令已被取入流水线。如果分支发生,这些预取的指令(称为分支延迟槽)需要被作废,导致性能损失。MIPS架构采用了分支延迟槽的设计,要求编译器在分支指令后填充一条无论分支是否发生都必须执行的指令,以部分隐藏分支开销。更现代的实现则采用动态分支预测等技术。

3. MIPS流水线在计算机系统中的地位

MIPS流水线不仅是处理器微架构的典范,也是理解现代高性能CPU设计(如超标量、乱序执行)的基石。在计算机系统的整体视角下:

- 硬件/软件接口:MIPS规整的指令集和流水线设计,简化了编译器的优化工作(如调度指令填充延迟槽、减少数据依赖)。

- 性能分析:它为计算机体系结构中的核心性能指标(如吞吐量、加速比)提供了直观的教学模型。

- 更高级技术的基础:多发射(每个周期发射多条指令)、动态调度等技术,可以视为对基本MIPS流水线的扩展和复杂化,以进一步挖掘指令级并行(ILP)。

4.

MIPS五级流水线以其结构清晰、教学性强的特点,成为了计算机系统结构学习中不可或缺的经典模型。它完美诠释了如何通过重叠执行来提升性能,同时也揭示了实现高效流水线所必须解决的冒险问题。理解MIPS流水线的工作机制、冒险成因及解决方案,是掌握现代处理器设计精髓的关键一步,为我们分析和理解更复杂的计算机系统奠定了坚实的理论基础。

如若转载,请注明出处:http://www.deshudiban.com/product/64.html

更新时间:2026-04-14 19:43:07